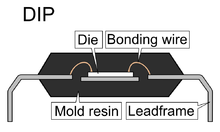

Integrinis grandynas (dažniau vadinamas integrine schema, mikroschema, silicio lustu, kompiuterio lustu arba mikroschema) – tai specialiai paruošto silicio (arba kito puslaidininkio) gabalėlis, į kurį fotolitografijos būdu išgraviruojama elektroninė schema. Silicio mikroschemose gali būti loginiai vartai, kompiuterių procesoriai, atmintis ir specialūs įtaisai. Mikroschema yra trapi ir jautri aplinkos poveikiui, todėl ją dažnai uždengia apsauginė plastikinė pakuotė arba metalinis korpusas. Elektrinis ryšys su mikroschema paprastai užtikrinamas plonais laidais (wire bonding) arba tiesioginiu litavimu prie kontaktų; šie laidai sujungia lustą su metaliniais kaiščiais ar kontaktų plokšte, per kurią lustas integruojamas į platesnį elektroninį įrenginį.

Kaip gaminama integrinė grandinė?

Gamybos procesas prasideda nuo plono silicio disko – plokštelės (wafer). Ant plokštelės atliekami keli pagrindiniai etapai: oksidacija, plonasluoksnių medžiagų nusodinimas, fotolitografijos procesai, dopinimas (jonų implantacija), etch (rievių išgraviravimas), metalo sluoksnių dengimas, testavimas ir galutinis pjaustymas (dicing). Fotolitografijos metu per šabloną (maskę) šviesa selektyviai aktyvuoja arba apsaugo tam tikras zonas, taip sukuriant labai smulkias grandinės struktūras. Po gamybos kiekvienas paruoštas lustas išbandomas (wafer testing), o po to atskiri lustai (die) supakuojami ir patikrinami dar kartą (final testing).

Pakuotės, jungtys ir montavimo būdai

Mikroschemų pakuotės tipai yra labai įvairūs: nuo senesnių DIP (Dual In-line Package) iki plokščių SMD (Surface-Mount Device) pakuočių, tokių kaip QFP, SOIC ir moderniausių BGA (Ball Grid Array). Pakuotė apsaugo lustą nuo mechaninių pažeidimų, drėgmės ir elektrostatinio iškrovimo, taip pat padeda šilumos išsklaidymui. Jungtys gali būti metaliniai kaiščiai, luiteliai ar litavimo kamuoliukai (BGA). Taip pat taikomi flip-chip metodai, kai lustas montuojamas tiesiogiai ant plokštės paviršiaus, sumažinant laidų ilgį ir paspartinant signalų perdavimą.

Tipai ir paskirtis

Integriniai grandynai skirstomi pagal funkcijas ir signalų pobūdį. Jie gali būti:

- analoginius – skirti nuolatiniams (nepertraukiamiems) signalams tvarkyti, pavyzdžiui, stiprintuvai, matavimo grandinės;

- skaitmeninius – dirbančius su dviejų lygių (0/1) signalais: loginiai elementai, procesoriai, skaičiavimo vienetai;

- mišrių signalų (analoginiai ir skaitmeniniai tame pačiame luste) – dažnai naudojami garso, radijo ir matavimo įrangai, kur reikia užtikrinti tiek analoginę, tiek skaitmeninę apdorojimo grandinę;

- specializuotus prietaisus: ASIC (application-specific integrated circuit), FPGA (programuojamos logikos matrica), mikrovaldiklius (MCU) ir SoC (system on chip), kuriuose viename luste sujungiamos kelios funkcijos.

Mikroschemos gali būti sukurtos labai konkrečiam uždaviniui – pavyzdžiui, skaičiuotuvui, arba būti bendros paskirties („universalūs“ logikos elementai ar atminties lustai). Atminties ir loginės struktūros bei procesoriai dažnai derinami kuriant sudėtingus elektroninius įrenginius.

Privalumai ir trūkumai

Privalumai:

- Maža kaina dėl masinės gamybos: daug komponentų telpa į vieną lustą, todėl vieneto savikaina mažėja;

- Didelis našumas: trumpesni signalų keliai – greitesnis veikimas ir mažesni energijos nuostoliai;

- Mažas dydis ir svoris – leidžia kurti kompaktiškus įrenginius;

- Aukštesnis patikimumas – mažiau jungčių tarp atskirų komponentų reiškia mažiau gedimų vietų.

Trūkumai ir iššūkiai:

- Šilumos valdymas – dideli integracijos laipsniai lemia intensyvesnį šilumos išsklaidymą ir reikalauja efektyvių aušinimo sprendimų;

- Aukštos pradinių investicijų sąnaudos (NRE – non-recurring engineering) kuriant naują lustą, ypač ASIC;

- Jautrumas elektrostatiniam iškrovimui (ESD) ir mechaniniams poveikiams;

- Technologinių ribų iššūkiai: miniatiūrizacija reikalauja pažangių litografijos technologijų (pvz., EUV) ir naujų medžiagų.

Ateities tendencijos

Technologijos vystosi link didesnės integracijos ir naujų architektūrų: 3D lustų sujungimas, System-on-Chip (SoC) sprendimai, pažangios litografijos priemonės ir naujos puslaidininkių medžiagos (pvz., SiC, GaN). Nors Moore’o dėsnis lėtėja, gamintojai ieško būdų, kaip išlaikyti spartą ir energijos efektyvumą, integruojant funkcijas ir tobulinant šilumos valdymą.