Superskalarinis procesorius: apibrėžimas, architektūra ir veikimas

Superskalarinis procesorius: apibrėžimas, architektūra ir veikimas — kaip instrukcijų lygiagretinimas ir funkcinių blokų dubliavimas ženkliai didina CPU našumą.

Superskalarinio procesoriaus konstrukcija leidžia viename procesoriuje taikyti lygiagrečiųjų skaičiavimų formą, vadinamą instrukcijų lygmens lygiagretinimu, todėl tuo pačiu taktiniu dažniu galima atlikti daugiau darbų. Tai reiškia, kad CPU per taktinį ciklą vykdo daugiau nei vieną instrukciją, vykdydamas kelias instrukcijas vienu metu (vadinama instrukcijų siuntimu) dubliuojamuose funkciniuose blokuose. Kiekvienas funkcinis blokas yra procesoriaus branduolio viduje esantis vykdymo resursas, pavyzdžiui aritmetinis loginis blokas (ALU), slankiojo kablelio blokas (FPU), bitų keitiklis arba daugiklis.

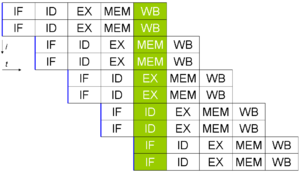

Dauguma superskalarinių procesorių taip pat yra su vamzdeliu (pipeline), tačiau gali būti ir superskalarinių procesorių be vamzdelio arba su vamzdeliu ne superskalarinių procesorių. Vamzdelio mechanizmas padeda padalinti instrukcijos vykdymą į etapus (pvz., nuskaitymas, dekodavimas, vykdymas, rezultatų rašymas), o superskalarumas leidžia atlikti kelis tokio tipo etapus lygiagrečiai skirtingoms instrukcijoms.

Kaip veikia superskalarus procesorius

Superskalarinį metodą palaiko kelios procesoriaus branduolio savybės:

- Instrukcijos pateikiamos iš užsakto instrukcijų sąrašo (fetch) ir dekoduojamos.

- Procesoriaus techninė įranga gali nustatyti, kurios instrukcijos turi kokią duomenų priklausomybę ir ar jas galima vykdyti lygiagrečiai.

- Per vieną taktinį ciklą gali būti perskaityta ir pateikta kelioms vykdymo grandims daugiau nei viena instrukcija (issue).

Kiekviena skaliarinio procesoriaus vykdoma instrukcija vienu metu keičia vieną ar du duomenų elementus, o kiekviena vektorinio procesoriaus vykdoma instrukcija vienu metu keičia daug duomenų elementų. Superskalarinis procesorius yra šių dviejų požiūrių mišinys:

- Kiekviena instrukcija apdoroja vieną duomenų elementą.

- Kiekviename procesoriaus branduolyje yra keli dubliuojantys funkciniai vienetai, todėl kelios instrukcijos vienu metu apdoroja nepriklausomus duomenų elementus.

Superskalariniame procesoriuje instrukcijų dispečeris nuskaito instrukcijas iš atminties, analizuoja jų priklausomybes ir nusprendžia, kurias iš jų galima vykdyti lygiagrečiai. Dispečeris išsiunčia tas instrukcijas į daugybę dubliuojančių funkcinių blokų, esančių procesoriaus viduje, taip bandydamas maksimizuoti užimtumą ir momentinį našumą (IPC — instrukcijų per ciklą skaičius).

Vykdymo etapai ir technikos

Svarbiausi etapai ir technikos, leidžiančios efektyviai išnaudoti superskalarumą:

- Fetch / Decode: nuskaitymas ir dekodavimas kelių instrukcijų vienu metu.

- Issue: dispečeris sprendžia, kurios instrukcijos gali būti išsiųstos į laisvus funkcinio vienetus.

- Register renaming: registrų pervadinimas pašalina tariamas (false) priklausomybes (WAR, WAW), leidžiant vykdyti daugiau instrukcijų lygiagrečiai.

- Reservation stations / Tomasulo algoritmas: rezervacijos stotys ir dinamines vykdymo planavimo schemos leidžia vykdyti instrukcijas iš eilės (out-of-order), kai tik yra reikalingi operandai.

- Reorder Buffer (ROB): užtikrina, kad rezultatų įrašymas atmintyje arba registruose įvyktų teisinga tvarka (commit), išlaikant programos matomą seką.

- Branch prediction: šakų spėjimas sumažina kontrolinius vėlavimus, leidžia palaikyti pilną vykdymo grandinę net prie šakų.

Priklausomybės ir konfliktai (hazardai)

Pagrindinės kliūtys, mažinančios superskalarinio procesoriaus efektyvumą:

- Duomenų priklausomybės: kai instrukcija laukia ankstesnės instrukcijos rezultato (RAW). Jas mažina registrų pervadinimas ir out-of-order vykdymas.

- Struktūriniai konfliktai: kai kelioms instrukcijoms reikia to paties funkcinio bloko tuo pačiu metu.

- Kontrolės (šakų) priklausomybės: šakų spėjimo klaidos verčia nutraukti ar išvalyti vamzdelius, kas kainuoja ciklus.

Superskalarumas vs kitos paradigmės

Superskalarumas skiriasi nuo kitų paralelizmo formų:

- Skaliarinis vs vektoriniai procesoriai: skaliarinė instrukcija apdoroja vieną duomenų elementą, vektorinė — daug elementų vienu metu. Superskalarus procesorius leidžia vienu metu vykdyti kelias skaliarines instrukcijas, taigi jis yra tarsi tarpinis sprendimas.

- VLIW (Very Long Instruction Word): VLIW perkelia sprendimą apie lygiagretinimą į kompiliatorių — instrukcijų paketas nurodo lygiagretumą statinėi, o ne dinamiškai dispečeriui. Superskalaras sprendžia daugumą klausimų dinamiškai aparatūros lygmenyje.

- Multicore: daug branduolių (multicore) suteikia lygiagretinimą aukštesniu lygiu (mėgėjų / užduočių lygiu), o superskalarumas vyksta viduje atskiro branduolio (instrukcijų lygmens lygiagretinimas).

Našumas, įgyvendinimas ir ribotumai

Projektuojant superskalarinį procesorių siekiama padidinti instrukcijų dispečerio tikslumą ir užtikrinti, kad daugybė funkcinių blokų būtų nuolat užimti. Nuo 2008 m. visi bendrosios paskirties procesoriai praktikoje dažnai naudoja superskalarines technikas; tipiniame superskalariniame procesoriuje gali būti kelios ALU, FPU ir SIMD vienetai (pvz., iki 4 ALU, 2 FPU ir du SIMD vienetai, priklausomai nuo dizaino). Aukštesnės klasės šiuolaikiniai procesoriai gali turėti dar platesnį išsiuntimo plotį (issue width), daugiau vykdymo vienetų ir sudėtingesnę dispečerio logiką.

Tačiau didesnis superskalarumas reiškia:

- didesnę aparatūros sudėtingumą (daugiau dispečerio logikos, didesnės rezervacijos struktūros, sudėtingesnis registrų pervadinimas);

- didesnes energijos sąnaudas ir šiluminį krūvį;

- mažėjančią grąžą — dėl priklausomybių ir šakų klaidų realus IPC dažnai labai toli nuo teorinio maksimumo;

- didėjančius kaštus ir diegimo riziką projektavimo metu.

Istorija ir praktika

Superskalarumas pradėtas plačiau diegti ir tobulinti XX a. pabaigoje ir per pastaruosius dešimtmečius tapo įprasta daugelio x86, ARM ir kitų architektūrų savybe. Įvairios įmonės — Intel, AMD, ARM ir kt. — diegia skirtingus kompromisus tarp išsiuntimo pločio, rezervacijos vietų, registrų pervadinimo ir šakų spėjimo tikslumo, atsižvelgdamos į našumą, energijos suvartojimą ir kaštus.

Santrauka

Superskalarinis procesorius yra efektyvus būdas padidinti vieno branduolio našumą, leidžiantis vykdyti kelias instrukcijas vienu metu naudojant daug dubliuotų vykdymo vienetų ir sudėtingą dispečerio logiką. Norint gauti gerą realų pranašumą, dizaineriai naudoja įvairias technikas: register renaming, out-of-order vykdymą, rezervacijos stotis, reorder buffer ir pažangų šakų spėjimą. Tačiau didesnis superskalarumas kelia techninių ir energetinių iššūkių, todėl dizaino sprendimai visuomet yra kompromisas tarp našumo, sudėtingumo ir energijos vartojimo.

Projektuojant superskalarinį procesorių svarbu rasti pusiausvyrą tarp dispečerio sudėtingumo, funkcinio blokų skaičiaus ir energijos efektyvumo — tik tada daugelis funkcinių blokų išliks užimti ir bus pasiektas aukštas realus našumas.

Paprastas superskalarinis vamzdynas. Imant ir siunčiant po dvi instrukcijas vienu metu, per ciklą galima atlikti ne daugiau kaip dvi instrukcijas.

CRAY T3e lygiagrečiojo kompiuterio procesoriaus plokštė su keturiais superskalariniais Alpha procesoriais

Apribojimai

Superscalar procesorių našumo didinimą riboja du dalykai:

- Instrukcijų sąraše integruoto lygiagretumo lygis

- Dispečerio ir duomenų priklausomybės tikrinimo sudėtingumas ir laiko sąnaudos.

Net jei įprastame superskalariniame procesoriuje priklausomybių tikrinimas būtų be galo spartus, jei pats instrukcijų sąrašas turi daug priklausomybių, tai taip pat apribotų galimą našumo padidėjimą, todėl dar vienas apribojimas yra kode integruoto lygiagretumo kiekis.

Nesvarbu, koks didelis būtų dispečerio greitis, yra praktinė riba, kiek instrukcijų galima išsiųsti vienu metu. Nors techninės įrangos pažanga leis sukurti daugiau funkcinių vienetų (pvz., ALU) viename procesoriaus branduolyje, instrukcijų priklausomybių tikrinimo problema padidėja tiek, kad pasiekiama superskalarinio dispečerinio dispečerio riba yra šiek tiek mažesnė. Tikėtina, kad vienu metu siunčiamos penkios-šešios instrukcijos.

Alternatyvos

- Vienalaikis daugiagretis duomenų srautų valdymas (angl. Simultaneous multithreading), dažnai sutrumpintai vadinamas SMT, - tai metodas, kuriuo siekiama padidinti bendrą superskalarinių procesorių spartą. SMT leidžia vykdyti kelis nepriklausomus vykdymo srautus, kad būtų geriau išnaudojami šiuolaikinio superskalarinio procesoriaus turimi ištekliai.

- Daugiabranduoliai procesoriai: superskalariniai procesoriai nuo daugiabranduolinių procesorių skiriasi tuo, kad keli pertekliniai funkciniai vienetai nėra ištisi procesoriai. Vieną superskalarų procesorių sudaro pažangūs funkciniai blokai, tokie kaip ALU, sveikųjų skaičių daugiklis, sveikųjų skaičių keitiklis, slankiojo kablelio blokas (FPU) ir kt. Gali būti kelios kiekvieno funkcinio bloko versijos, kad būtų galima lygiagrečiai vykdyti daug instrukcijų. Tuo skiriasi nuo daugiabranduolinių procesorių, kurie vienu metu apdoroja instrukcijas iš kelių gijų, po vieną giją viename branduolyje.

- Vamzdeliniai procesoriai: superskalariniai procesoriai taip pat skiriasi nuo procesorių su vamzdynais, kuriuose kelios instrukcijos vienu metu gali būti įvairiuose vykdymo etapuose.

Įvairūs alternatyvūs metodai nėra vienas kitam prieštaraujantys - jie gali būti (ir dažnai yra) derinami viename procesoriuje, todėl galima sukurti daugiabranduolį procesorių, kuriame kiekvienas branduolys yra nepriklausomas procesorius su keliais lygiagrečiais superskalariniais vamzdynais. Kai kuriuose daugiabranduoliniuose procesoriuose taip pat yra vektorių funkcija.

Susiję puslapiai

- Lygiagretieji skaičiavimai

- Instrukcijų lygmens lygiagretumas

- Vienalaikis daugiasluoksniškumas (SMT)

- Daugiabranduoliai procesoriai

Klausimai ir atsakymai

K: Kas yra superskalarinė technologija?

A.: Superskalarinė technologija yra pagrindinių lygiagrečiųjų skaičiavimų forma, leidžianti per kiekvieną taktinį ciklą apdoroti daugiau nei vieną instrukciją, vienu metu naudojant kelis vykdymo vienetus.

K: Kaip veikia superskalarinė technologija?

A: Superskalarinė technologija apima instrukcijas, kurios į procesorių patenka eilės tvarka, ieškant duomenų priklausomybės, ir įkraunant daugiau nei vieną instrukciją per kiekvieną taktinį ciklą.

K: Kuo skiriasi skaliariniai ir vektoriniai procesoriai?

A.: Skalariniame procesoriuje instrukcijos paprastai vienu metu dirba su vienu ar dviem duomenų elementais, o vektoriniame procesoriuje instrukcijos paprastai vienu metu dirba su daugeliu duomenų elementų. Superskalarinis procesorius yra abiejų tipų mišinys, nes kiekviena instrukcija apdoroja vieną duomenų elementą, tačiau vienu metu vykdoma daugiau nei viena instrukcija, todėl procesorius vienu metu apdoroja daug duomenų elementų.

Klausimas: Kokį vaidmenį superskalariniame procesoriuje atlieka tikslus instrukcijų dispečeris?

A: Tikslus instrukcijų dispečeris yra labai svarbus superskalariniam procesoriui, nes užtikrina, kad vykdymo vienetai visada būtų užimti darbais, kurių greičiausiai prireiks. Jei instrukcijų dispečeris nėra tikslus, dalį darbo gali tekti išmesti, todėl procesorius nebus greitesnis už skaliarinį procesorių.

Klausimas: Kuriais metais visi įprasti procesoriai tapo superskalariniais?

A: 2008 m. visi įprasti procesoriai tapo superskaliniais.

K: Kiek ALU, FPU ir SIMD blokų gali būti įprastame procesoriuje?

A: Įprastame centriniame procesoriuje gali būti iki 4 ALU, 2 FPU ir 2 SIMD vienetai.

Ieškoti